1.1W Mono Low-Voltage Audio Power Amplifier

### Features

- Operating Voltage : 2.6V-5.5V

- APA0713 Compatible with TPA751

- Supply Current

- $-I_{DD}$ =1.3mA at V<sub>DD</sub>=5V ,BTL mode

- I<sub>DD</sub>=0.9mA at V<sub>DD</sub>=3.3V ,BTL mode

- Low Shutdown Current

- I<sub>DD</sub>=0.1mA

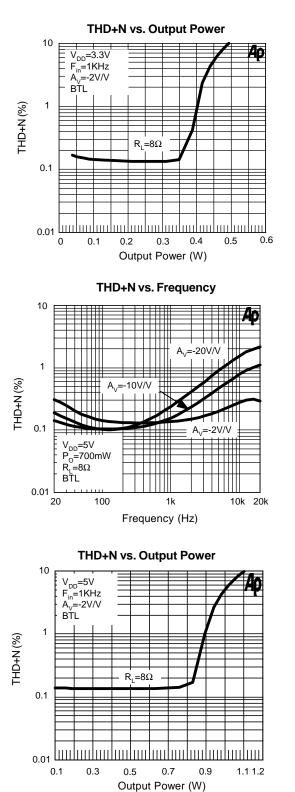

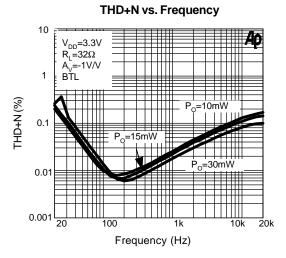

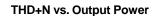

- Low Distortion

630mW, at V<sub>DD</sub>=5V, BTL, R<sub>L</sub>=8W

THD+N=0.15%

280mW, at V<sub>DD</sub>=3.3V, BTL, R<sub>L</sub>=8W

THD+N=0.15%

- Output Power

- at 1% THD+N

- 900mW, at  $V_{DD}$ =5V, BTL, R<sub>L</sub>=8W

- 400mW, at  $V_{DD}$ =3.3V, BTL, R<sub>L</sub>=8W

- at 10% THD+N

- 1.1W at  $V_{DD}$ =5V, BTL, R<sub>L</sub>=8W

- 480mW at  $V_{DD}$ =3.3V, BTL, R<sub>L</sub>=8W

- Depop Circuitry Integrated

- Thermal Shutdown Protection and Over Current Protection Circuitry

- High supply voltage ripple rejection

- Surface-Mount Packaging

8 pin SOP

- Lead Free Available (RoHS Compliant)

### **General Description**

The APA0713 is a bridged-tied load (BTL) audio power amplifier developed especially for low-voltage applications where internal speakers operation is required. Operating with a 5V supply, the APA0713 can deliver 1.1W of continuous power into a BTL 8Ω load at 10% THD+N throughout voice band frequencies. Although this device is characterized out to 20kHz, its operation is optimized for narrow band applications such as wireless communications. The BTL configuration eliminates the need for external coupling capacitors on the output in most applications, which is particularly important for small battery-powered equipment. This device features a shutdown mode for power-sensitive applications with special depop circuitry to eliminate speaker noise when exiting shutdown mode. The APA0713 is available in8-pin SOP.

### **Applications**

- Mobil Phones

- PDAs

- Digital Cameras

- Portable Electronic Devices

## Ordering and Marking Information

| APA0713                           | Package Code<br>K : SOP-8<br>Temperature Range<br>I : -40 to 85 °C<br>Handling Code<br>TR : Tape & Reel<br>Assembly Material<br>G : Halogen and Lead Free Device |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APA0713 K : APA0713<br>XXXXX<br>• | XXXXX - Date Code                                                                                                                                                |

Note : ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight).

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

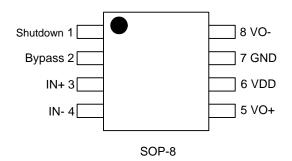

## **Pin Configuration**

## **Absolute Maximum Ratings**

(Over operating free-air temperature range unless otherwise noted.)

| Symbol           | Parameter                              | Rating                       | Unit |

|------------------|----------------------------------------|------------------------------|------|

| V <sub>DD</sub>  | Supply Voltage                         | -0.3 to 6                    | V    |

| V <sub>IN</sub>  | Input Voltage Range, Shutdown, SE/BTL  | -0.3 to V <sub>DD</sub> +0.3 | V    |

| T <sub>A</sub>   | Operating Ambient Temperature Range    | -40 to 85                    | °C   |

| TJ               | Maximum Junction Temperature           | Internally Limited*1         | °C   |

| T <sub>STG</sub> | Storage Temperature Range              | -65 to +150                  | °C   |

| T <sub>SDR</sub> | Lead Soldering Temperature, 10 seconds | 260                          | °C   |

| P <sub>D</sub>   | Power Dissipation                      | Internally Limited           | W    |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2 : APA0713 starts its internal thermal shutdown protection when junction temperature ramps up to 170°C.

### **Recommended Operating Conditions**

| Symbol          | Parameter          | Test Conditions | Min. | Max. | Unit |

|-----------------|--------------------|-----------------|------|------|------|

| V <sub>DD</sub> | Supply Voltage     |                 | 2.6  | 5.5  | V    |

| V <sub>IH</sub> | High-Level Voltage | Shutdown        | 2.2  |      | V    |

| V <sub>IL</sub> | Low-Level Voltage  | Shutdown        |      | 0.4  | V    |

### **Thermal Characteristics**

| Symbol            | Parameter                                               | Value | Unit |

|-------------------|---------------------------------------------------------|-------|------|

| R <sub>THJA</sub> | Thermal Resistance from Junction to Ambient in Free Air |       | °C/W |

| I THIA            | SOP-8 <sup>(Note 2)</sup>                               | 200   | 0/11 |

Note 2: 3.42in<sup>2</sup> printed circuit board with 20z trace and copper.

### **Electrical Characteristics**

#### Electrical Characteristics at Specified Free - Air Temperature

$V_{DD}$  = 3.3V,  $T_{A}$  = 25°C (unless otherwise noted)

| Symbol              | Parameter                                        | Test Conditions                            | APA0713 |      |      | Unit    |  |

|---------------------|--------------------------------------------------|--------------------------------------------|---------|------|------|---------|--|

| Symbol              |                                                  |                                            | Min.    | Тур. | Max. | onit    |  |

| Vos                 | Output Offset Voltage                            | $R_L = 8\Omega, R_F = 10k\Omega$           |         |      | 20   | mV      |  |

| I <sub>DD</sub>     | Supply Current                                   | BTL mode, $R_F = 10k\Omega$                |         | 0.9  | 1.8  | mA      |  |

| I <sub>DD(SD)</sub> | Supply Current, Shutdown Mode                    | $R_F = 10k\Omega$                          |         | 0.1  | 2    | μA      |  |

| IH                  |                                                  | Shutdown, $V_I = V_{DD}$                   |         |      | 1    | μA      |  |

| IL                  |                                                  | Shutdown, $V_I = 0V$                       |         |      | 1    | μA      |  |

| Operating           | characteristic, $V_{DD}$ = 3.3V, $T_A$ = 25°C, R | RL = 8W                                    |         |      |      |         |  |

| Po                  | Output Power (Note 3)                            | THD+N = 1%, BTL mode, $R_L = 8\Omega$      |         | 400  |      | mW      |  |

| го                  |                                                  | THD+N = 1%, BTL mode, $R_L = 4\Omega$      |         | 600  |      | 11100   |  |

| THD+N               | Total Harmonic Distortion Plus Noise             | $P_0 = 280$ mW, BTL mode, $R_L = 8\Omega$  |         | 0.15 |      | %       |  |

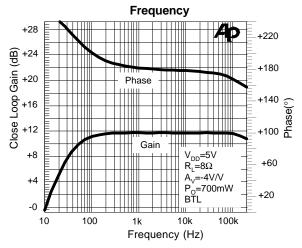

| Bom                 | Maximum Output Power Bandwidth                   | Gain = 2, THD+N = 2%                       |         | 20   |      | KHz     |  |

| B1                  | Unity-Gain Bandwidth                             | Open Loop                                  |         | 2    |      | MHz     |  |

| PSRR                | Power Supply Rejection Ratio (Note1)             | $C_B = 1\mu F$ , BTL mode, $R_L = 8\Omega$ |         | 74   |      | dB      |  |

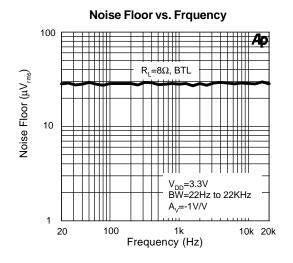

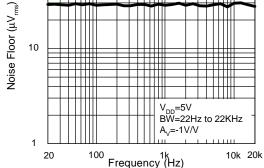

| Vn                  | Noise Output Voltage                             | Gain = 1, $C_B = 0.1 \mu F$                |         | 28   |      | μV(rms) |  |

| Twu                 | Wake-up time                                     | $C_B = 1\mu F$                             |         | 380  |      | ms      |  |

$V_{DD}$ = 5V,  $T_{A}$ = 25°C (unless otherwise noted)

| Symbol              | Parameter                                                      | Test Conditions                              |      | 11:0:14 |      |         |

|---------------------|----------------------------------------------------------------|----------------------------------------------|------|---------|------|---------|

| Symbol              | Parameter                                                      | Test Conditions                              | Min. | Тур.    | Max. | - Unit  |

| Vos                 | Output Offset Voltage                                          | $R_L = 8\Omega, R_F = 10K\Omega$             |      |         | 20   | mV      |

| I <sub>DD</sub>     | Supply Current                                                 | BTL mode, $R_F = 10 \text{ K}\Omega$         |      | 1.3     | 2.6  | m /     |

|                     | Supply Current                                                 | SE mode, $R_F = 10 \text{ K}\Omega$          |      | 0.75    | 1.5  | - mA    |

| I <sub>DD(SD)</sub> | Supply Current, Shutdown Mode                                  | R <sub>F</sub> = 10 KΩ                       |      | 0.1     | 2    | μΑ      |

| IH                  |                                                                | Shutdown, $V_I = V_{DD}$                     |      |         | 1    | μA      |

| IL                  |                                                                | Shutdown, $V_1 = 0V$                         |      |         | 1    | μA      |

| Operating           | characteristic, V <sub>DD</sub> = 5V, T <sub>A</sub> = 25°C, F | R∟ = 8W                                      |      |         |      | ÷       |

| Po                  | Output Power (Note 3)                                          | THD+N = 1%, BTL mode, $R_L = 8\Omega$        |      | 900     |      | mW      |

| 10                  |                                                                | THD+N = 1%, BTL mode, $R_L = 4\Omega$        |      | 1.5     |      | W       |

| THD+N               | Total Harmonic Distortion Plus Noise                           | $P_0 = 630$ mW, BTL mode,<br>$R_L = 8\Omega$ |      | 0.15    |      | %       |

| Bom                 | Maximum Output Power Bandwidth                                 | Gain = 2, THD+N = 2%                         |      | 20      |      | KHz     |

| B1                  | Unity-Gain Bandwidth                                           | Open Loop                                    |      | 2       |      | MHz     |

| PSRR                | Power Supply Rejection Ratio (Note 3)                          | $C_B = 1\mu F$ , BTL mode, $R_L = 8\Omega$   |      | 74      |      | dB      |

| Vn                  | Noise Output Voltage                                           | Gain = 1, $C_B = 0.1 \mu F$                  |      | 28      |      | μV(rms) |

| Twu                 | Wake-up time                                                   | С <sub>в</sub> = 1μF                         |      | 400     |      | ms      |

Note 3 : Output power is measured at the output terminals of device at f=1KHz.

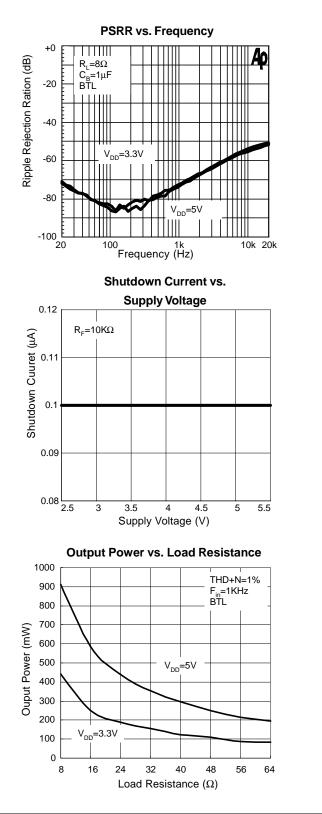

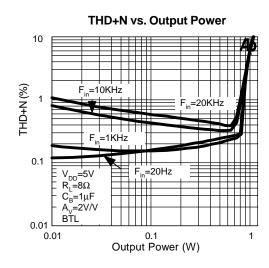

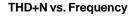

## **Typical Operating Characteristics**

Copyright © ANPEC Electronics Corp. Rev. A.2 - Apr., 2012 Frequency (Hz)

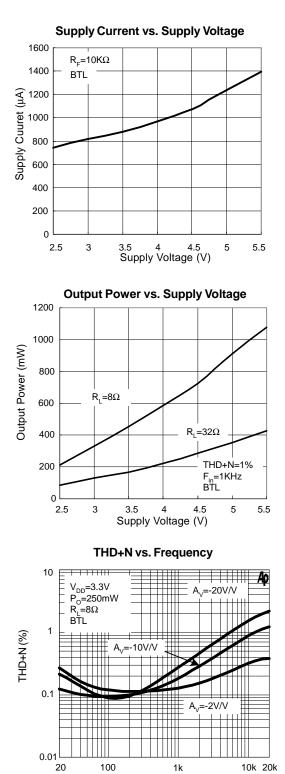

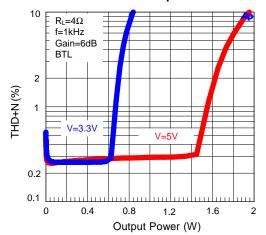

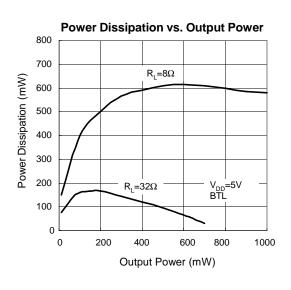

# Typical Operating Characteristics (Cont.)

Copyright © ANPEC Electronics Corp. Rev. A.2 - Apr., 2012

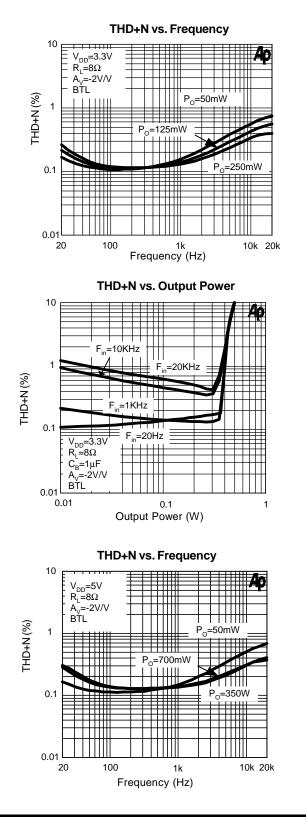

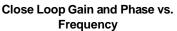

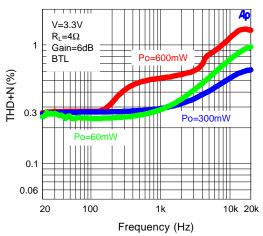

# **Typical Operating Characteristics (Cont.)**

Close Loop Gain and Phase vs.

Copyright © ANPEC Electronics Corp. Rev. A.2 - Apr., 2012

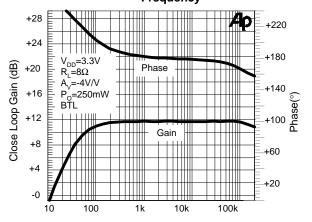

## Typical Operating Characteristics (Cont.)

Copyright © ANPEC Electronics Corp. Rev. A.2 - Apr., 2012

THD+N vs. Frequency

# **Pin Descriptions**

| Pin      |    | 1/0 | Description                                                                          |

|----------|----|-----|--------------------------------------------------------------------------------------|

| Name     | No | I/O | Description                                                                          |

| Shutdown | 1  | Ι   | Shutdown mode control signal input, place entire IC in shutdown mode when held high. |

| Bypass   | 2  | Ι   | Bypass pin                                                                           |

| IN+      | 3  | Ι   | IN+ is the non-inverting input. IN+ is typically tied to the Bypass terminal.        |

| IN-      | 4  | Ι   | IN- is the inverting input. IN- is typically used as the audio input terminal.       |

| VO+      | 5  | 0   | VO+ is the positive BTL output.                                                      |

| VDD      | 6  |     | Supply voltage input pin.                                                            |

| GND      | 7  |     | Ground connection for circuitry.                                                     |

| VO-      | 8  | 0   | VO- is the negative BTL output.                                                      |

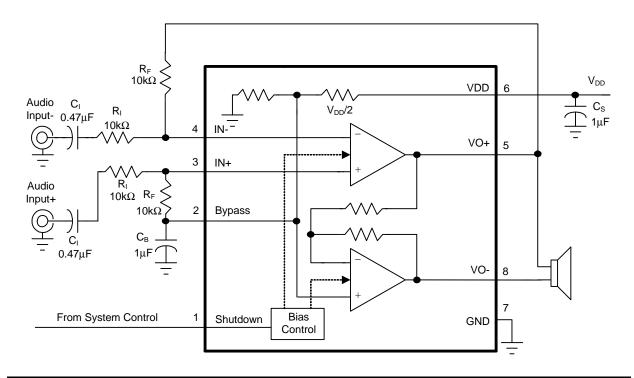

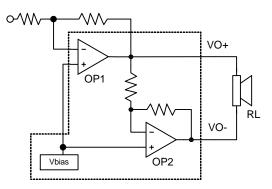

## **Block Diagram**

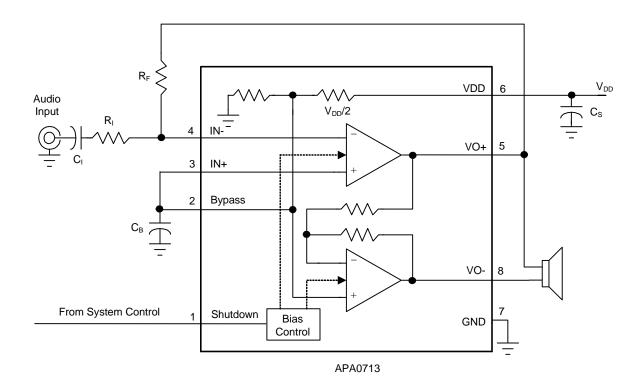

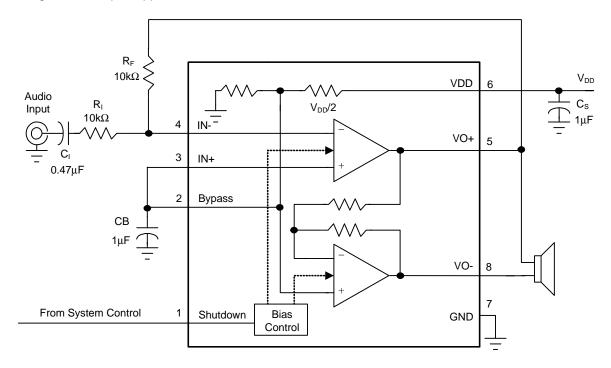

# **Typical Application Circuits**

For Single-ended Input Application

#### For Differential Input Application

### **Application Information**

#### **BTL Operation**

Figure 1: APA0713 power amplifier internal configuration

The power amplifier OP1 gain is set by external gain setting, while the second amplifier OP2 is internally fixed in a unity-gain, inverting configuration. Figure 1 shows that the output of OP1 is connected to the input to OP2, which results in the output signals of with both amplifiers with identical in magnitude, but out of phase 180°. Consequently, the differential gain for each channel is 2X (Gain of SE mode).

By driving the load differentially through outputs VO+ and VO-, an amplifier configuration commonly referred to as bridged mode is established. The BTL mode operation is different from the classical single-ended SE amplifier configuration where one side of its load is connected to ground.

The BTL amplifier design has a few distinct advantages over the SE configuration, as it provides differential drive to the load, thus doubling the output swing for a specified supply voltage.

Four times the output power is possible as compared with a SE amplifier under the same conditions. A BTL configuration, such as the one used in the APA0713, also creates a second advantage over SE amplifiers. Since the differential outputs, VO+ and VO-, are biased at halfsupply, no need DC voltage exists across the load. This eliminates the need for an output coupling capacitor which is required in a single supply, SE configuration.

#### Input Capacitor, C

In the typical application, an input capacitor,  $C_1$ , is required to allow the amplifier to bias the input signal to the proper DC level for optimum operation. In this case,  $C_1$ and the minimum input impedance  $R_1$  from a high-pass filter with the corner frequency are determined in the following equation :

$$Fc(highpass) = \frac{1}{2\pi R_1 C_1}$$

(1)

The value of C<sub>1</sub> is important to consider as it directly affects the low frequency performance of the circuit. Consider the example where R<sub>1</sub> is 100K $\Omega$  and the specification calls for a flat bass response down to 40Hz. Equation is reconfigured as followed :

$$C_{I} = \frac{1}{2\pi R_{I}F_{C}}$$

(2)

Consider input resistance variation, the C<sub>1</sub> is  $0.04\mu$ F so one would likely choose a value in the range of  $0.1\mu$ F to  $1.0\mu$ F.

A further consideration for this capacitor is the leakage path from the input source through the input network  $(R_1+R_F, C_1)$  to the load.

This leakage current creates a DC offset voltage at the input to the amplifier that reduces useful headroom, especially in high gain applications. For this reason, a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications as the DC level there is held at  $V_{DD}/2$ , which is likely higher than the source DC level. Please note that it is important to confirm the capacitor polarity in the application.

#### Effective Bypass Capacitor, C

As other power amplifiers, proper supply bypassing is critical for low noise performance and high power supply rejection.

The capacitors located on the bypass and power supply pins should be as close to the device as possible. The effect of a larger half supply bypass capacitor will improve

# Application Information (Cont.)

#### Effective Bypass Capacitor, C<sub>bypass</sub> (Cont.)

PSRR due to increased half-supply stability. Typical application employs a 5V regulator with  $1.0\mu$ F and a  $0.1\mu$ F bypass as supply filtering. This does not eliminate the need for bypassing the supply nodes of the APA0713. The selection of bypass capacitors, especially C<sub>bypass</sub>, thus depends upon desired PSRR requirements, click- and-pop performance.

To avoid start-up pop noise occurred, the bypass voltage should rise slower than the input bias voltage and the relationship shown in equation (4) should be maintained.

$$\frac{1}{C_{\text{bypass}} \times 80 \text{K}\Omega} \quad << \quad \frac{1}{(\text{R}_{\text{I}} + \text{R}_{\text{F}}) \times \text{C}_{\text{I}}} \tag{3}$$

The bypass capacitor is fed from a  $80K\Omega$  resistor inside the amplifier. Bypass capacitor,  $C_{bypass}$ , values of  $0.1\mu$ F to  $2.2\mu$ F ceramic or tantalum low-ESR capacitors are recommended for the best THD+N and noise performance.

The bypass capacitance also effects to the start up time. It is determined in the following equation :

$$T_{\text{startup}} = 5 \times (C_{\text{bypass}} \times 80 \text{K}\Omega) \tag{4}$$

#### Power Supply Decoupling, C<sub>s</sub>

The APA0713 is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD+N) is as low as possible. Power supply decoupling also prevents the oscillations causing by long lead length between the amplifier and the speaker. The optimum decoupling is achieved by using two different types of capacitors that target on different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalentseries-resistance (ESR) ceramic capacitor, typically 0.1µF, is placed as close as possible to the device's VDD lead, which is for the best performance. For filtering lower-frequency noise signals, a large aluminum electrolytic capacitor of 10µF or greater placed near the audio power amplifier is recommended.

#### **Optimizing Depop Circuitry**

Circuitry has been included in the APA0713 to minimize the amount of popping noise at power-up and when coming out of shutdown mode. Popping occurs whenever a voltage step is applied to the speaker. In order to eliminate click-and-pop, all capacitors must be fully discharged before turn-on. Rapid on/off switching of the device or the shutdown function will cause the click-andpop circuitry. The value of  $C_1$  will also affect turn-on pops (refer to Effective Bypass Capacitance). The bypass voltage rise up should be slower than input bias voltage.

Although the bypass pin current source cannot be modified, the size of  $C_{bypass}$  can be changed to alter the device turn-on time and the amount of click-and-pop. By increasing the value of  $C_{bypass}$ , turn-on pop can be reduced. However, the tradeoff for using a larger bypass capacitor is to increase the turn-on time for this device. There is a linear relationship between the size of  $C_{bypass}$  and the turnon time.

In the most cases, choosing a small value of  $C_1$  in the range of  $0.33\mu$ F to  $1\mu$ F,  $C_{bypass}$  being equal to  $1\mu$ F should produce a virtually clickless and popless turn-on.

A high gain amplifier intensifies the problem as the small delta in voltage is multiplied by the gain. Hence, it is advantageous to use low-gain configurations.

#### **Shutdown Function**

In order to reduce power consumption while not in using, the APA0713 contains a shutdown function to externally turn off the amplifier bias circuitry. This shutdown feature turns the amplifier off when a logic low on the Shutdown pin for APA0713.

The trigger point between a logic high and logic low level is typically  $0.4V_{\text{DD}}$ . It's better to switch between ground and the supply voltage  $V_{\text{DD}}$  to provide maximum device performance.

By switching the Shutdown pin to high level, the amplifier enters a low-current state,  $I_{DD}$  for APA0713. APA0713 is in shutdown mode. In normal operation, APA0713's Shutdown pin should be pulled to low level to keep the IC

# **Application Information (Cont.)**

#### **Shutdown Function (Cont.)**

out of the shutdown mode. The Shutdown pin should be tied to a definite voltage to avoid unwanted state changes.

#### **BTL Amplifier Efficiency**

An easy-to-use equation to calculate efficiency starts out as being equal to the ratio of power from the power supply to the power delivered to the load. The following equations are the basis for calculating amplifier efficiency.

$$Efficiency = \frac{P_O}{P_{SUP}}$$

(5)

Where

$$P_{O} = \frac{V_{orms} \times V_{orms}}{R_{L}} = \frac{(V_{P} \times V_{P})}{2R_{L}}$$

$$V_{orms} = \frac{V_{P}}{2R_{L}}$$

(6)

$$V_{orms} = \frac{V_P}{\sqrt{2}}$$

(6)

$$P_{SUP} = V_{DD} \times L_{DD, AVG} = V_{DD} \times \frac{2V_P}{\pi R_1}$$

(7)

$$\frac{P_{O}}{P_{SUP}} = \frac{\left(\frac{V_{P} \times V_{P}}{2R_{L}}\right)}{\left(V_{DD} \times \frac{2V_{P}}{\pi R_{L}}\right)} = \frac{\pi V_{P}}{4V_{DD}}$$

(8)

| Po (W) | Efficiency (%) | V <sub>P</sub> (V) | P <sub>D</sub> (W) |

|--------|----------------|--------------------|--------------------|

| 0.125  | 33.6           | 1.41               | 0.26               |

| 0.25   | 47.6           | 2.00               | 0.29               |

| 0.375  | 58.3           | 2.45*              | 0.28               |

\*High peak voltages cause the THD+N to increase.

Table 1. Efficiency vs. Output Power in  $3.3V/8\Omega$  BTL Systems.

Table 1 employs equation 8 to calculate efficiencies for three different output power levels when load is  $8\Omega$ .

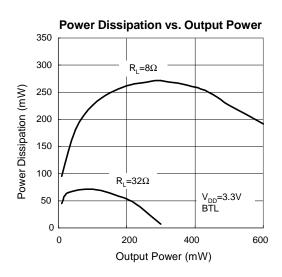

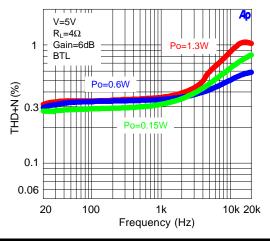

The efficiency of the amplifier is quite low for lower power levels and rises sharply as power to the load is increased resulting in a nearly flat internal power dissipation over the normal operating range. Note that the internal dissipation at full output power is less than in the half power range. Calculating the efficiency for a specific system is the key to proper power supply design. For a mono 900mW audio system with  $8\Omega$  loads and a 5V supply, the maximum draw on the power supply is almost 1.5W.

A final point to remember about linear amplifiers (either SE or BTL) is how to manipulate the terms in the efficiency equation to utmost advantage when possible. Note that in equation8,  $V_{DD}$  is in the denominator.

This indicates that as  $V_{\text{DD}}$  goes down, efficiency goes up. In other words, the efficiency analysis is used to choose the correct supply voltage and speaker impedance for the application.

#### **Power Dissipation**

Whether the power amplifier is operated in BTL or SE modes, power dissipation is a major concern. In equation9 states the maximum power dissipation point for a SE mode operating at a given supply voltage and driving a specified load.

SE mod e : P<sub>D, MAX</sub> =

$$\frac{V_{DD}^2}{2\pi^2 R_L}$$

(9)

In BTL mode operation, the output voltage swing is doubled as in SE mode. Thus the maximum power dissipation point for a BTL mode operating at the same given conditions is 4 times as in SE mode.

BTL mod e : P<sub>D, MAX</sub> =

$$\frac{4V_{DD}^2}{2\pi^2 R_L}$$

(10)

Since the APA0713 is a mono channel power amplifier, the maximum internal power dissipation is equal to the both of equations depending on the mode of operation. The power dissipation from equation10, assuming a 5V-power supply and an  $8\Omega$  load, must not be greater than the power dissipation that results from the equation11:

$$P_{D,MAX} = \frac{T_{J,MAX} - T_{A}}{\theta_{JA}}$$

(11)

# **Application Information (Cont.)**

#### Power Dissipation (Cont.)

For SOP-8 package, the thermal resistance ( $\theta_{JA}$ ) is equal to 200°C/W, respectively.

Since the maximum junction temperature  $(T_{J,MAX})$  of APA0713 is 170°C and the ambient temperature  $(T_A)$  is defined by the power system design, the maximum power dissipation which the IC package is able to handle can be obtained from equation 11. Once the power dissipation is greater than the maximum limit ( $P_{D,MAX}$ ), either the supply voltage ( $V_{DD}$ ) must be decreased, the load impedance ( $R_L$ ) must be increased, or the ambient temperature should be reduced.

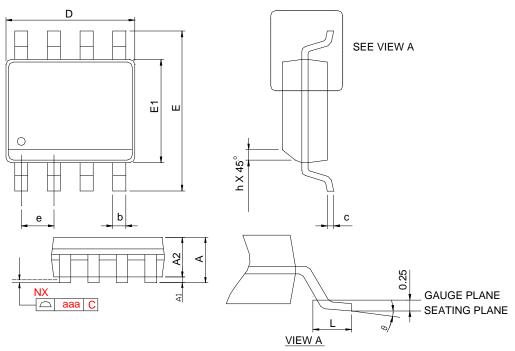

### **Package Information**

SOP-8

| S       |        | SO         | P-8   |            |

|---------|--------|------------|-------|------------|

| SY MBOL | MILLIM | ETERS      | INC   | IES        |

| L<br>C  | MIN.   | MAX.       | MIN.  | MAX.       |

| А       |        | 1.75       |       | 0.069      |

| A1      | 0.10   | 0.25       | 0.004 | 0.010      |

| A2      | 1.25   |            | 0.049 |            |

| b       | 0.31   | 0.51       | 0.012 | 0.020      |

| с       | 0.17   | 0.25       | 0.007 | 0.010      |

| D       | 4.80   | 5.00       | 0.189 | 0.197      |

| Е       | 5.80   | 6.20       | 0.228 | 0.244      |

| E1      | 3.80   | 4.00       | 0.150 | 0.157      |

| е       | 1.27   | BSC        | 0.050 | BSC        |

| h       | 0.25   | 0.50       | 0.010 | 0.020      |

| L       | 0.40   | 1.27       | 0.016 | 0.050      |

| θ       | 0°     | <b>8</b> ° | 0°    | <b>8</b> ° |

| aaa     | 0.1    | 10         | 0.0   | 04         |

Note: 1. Follow JEDEC MS-012 AA.

2. Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion or gate burrs shall not exceed 6 mil per side.

3. Dimension "E" does not include inter-lead flash or protrusions.

Inter-lead flash and protrusions shall not exceed 10 mil per side.

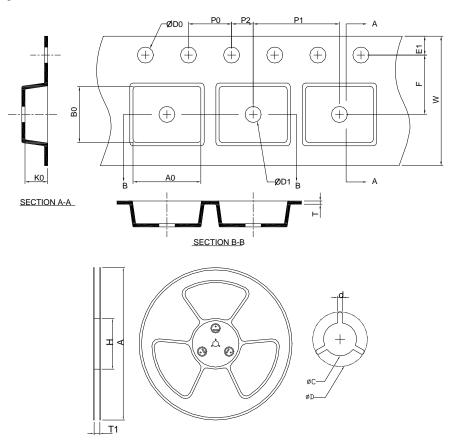

## **Carrier Tape & Reel Dimensions**

| Application | Α                 | Н                 | T1                 | С                  | d        | D                 | W                  | E1                 | F                 |

|-------------|-------------------|-------------------|--------------------|--------------------|----------|-------------------|--------------------|--------------------|-------------------|

|             | 330.0 £.00        | 50 MIN.           | 12.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 12.0 <b>±</b> 0.30 | 1.75 <b>±</b> 0.10 | 5.5 <b>±</b> 0.05 |

| SOP-8       | P0                | P1                | P2                 | D0                 | D1       | Т                 | A0                 | B0                 | K0                |

|             | 4.0 <b>±</b> 0.10 | 8.0 <b>±</b> 0.10 | 2.0 <b>±</b> 0.05  | 1.5+0.10<br>-0.00  | 1.5 MIN. | 0.6+0.00<br>-0.40 | 6.40 <b>±</b> 0.20 | 5.20 ±0.20         | 2.10 ±0.20        |

(mm)

### **Devices Per Unit**

| Package Type | Unit        | Quantity |

|--------------|-------------|----------|

| SOP-8        | Tape & Reel | 2500     |

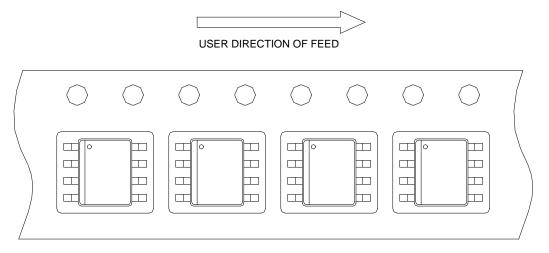

## **Taping Direction Information**

SOP-8

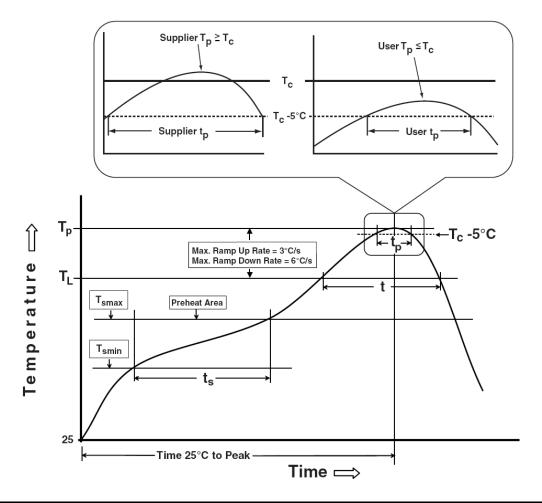

### **Classification Profile**

### **Classification Reflow Profiles**

| Profile Feature                                                                                                                                                                                                         | Sn-Pb Eutectic Assembly            | Pb-Free Assembly                   |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|--|--|

| <b>Preheat &amp; Soak</b><br>Temperature min (T <sub>smin</sub> )<br>Temperature max (T <sub>smax</sub> )<br>Time (T <sub>smin</sub> to T <sub>smax</sub> ) (t <sub>s</sub> )                                           | 100 °C<br>150 °C<br>60-120 seconds | 150 °C<br>200 °C<br>60-120 seconds |  |  |  |

| Average ramp-up rate<br>(T <sub>smax</sub> to T <sub>P</sub> )                                                                                                                                                          | 3 °C/second max.                   | 3°C/second max.                    |  |  |  |

| Liquidous temperature (T <sub>L</sub> )<br>Time at liquidous (t <sub>L</sub> )                                                                                                                                          | 183 °C<br>60-150 seconds           | 217 °C<br>60-150 seconds           |  |  |  |

| Peak package body Temperature<br>(T <sub>p</sub> )*                                                                                                                                                                     | See Classification Temp in table 1 | See Classification Temp in table 2 |  |  |  |

| Time $(t_P)^{**}$ within 5°C of the specified classification temperature $(T_c)$                                                                                                                                        | 20** seconds                       | 30** seconds                       |  |  |  |

| Average ramp-down rate ( $T_p$ to $T_{smax}$ )                                                                                                                                                                          | 6 °C/second max.                   | 6 °C/second max.                   |  |  |  |

| Time 25°C to peak temperature                                                                                                                                                                                           | 6 minutes max.                     | 8 minutes max.                     |  |  |  |

| * Tolerance for peak profile Temperature $(T_p)$ is defined as a supplier minimum and a user maximum.<br>** Tolerance for time at peak profile temperature $(t_p)$ is defined as a supplier minimum and a user maximum. |                                    |                                    |  |  |  |

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br><sup>3</sup> 350 |

|----------------------|--------------------------------|--------------------------------------------|

| <2.5 mm              | 235 °C                         | 220 °C                                     |

| ≥2.5 mm              | 220 °C                         | 220 °C                                     |

Table 2. Pb-free Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>350-2000 | Volume mm <sup>3</sup><br>>2000 |

|----------------------|--------------------------------|------------------------------------|---------------------------------|

| <1.6 mm              | 260 °C                         | 260 °C                             | 260 °C                          |

| 1.6 mm – 2.5 mm      | 260 °C                         | 250 °C                             | 245 °C                          |

| ≥2.5 mm              | 250 °C                         | 245 °C                             | 245 °C                          |

### **Reliability Test Program**

| Test item     | Method             | Description                  |

|---------------|--------------------|------------------------------|

| SOLDERABILITY | JESD-22, B102      | 5 Sec, 245°C                 |

| HOLT          | JESD-22, A108      | 1000 Hrs, Bias @ Tj=125°C    |

| PCT           | JESD-22, A102      | 168 Hrs, 100%RH, 2atm, 121°C |

| тст           | JESD-22, A104      | 500 Cycles, -65°C~150°C      |

| НВМ           | MIL-STD-883-3015.7 | VHBM 2KV                     |

| MM            | JESD-22, A115      | VMM 200V                     |

| Latch-Up      | JESD 78            | 10ms, 1 <sub>tr</sub> 100mA  |

### **Customer Service**

#### Anpec Electronics Corp.

Head Office : No.6, Dusing 1st Road, SBIP, Hsin-Chu, Taiwan Tel : 886-3-5642000 Fax : 886-3-5642050

Taipei Branch : 2F, No. 11, Lane 218, Sec 2 Jhongsing Rd., Sindian City, Taipei County 23146, Taiwan Tel : 886-2-2910-3838 Fax : 886-2-2917-3838